"Europe will not be made all at once, or according to a single plan. It will be built through concrete achievements which first create a de facto solidarity." Robert Schuman

# **WORKSHOP ON PHOTONICS**

Yves GIGASE

Head of Programmes

30 March 2022

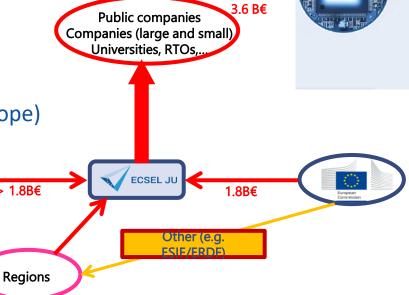

# **KDT JU 2021-2027**

- Third generation JU

- KDT JU = Key Digital Technology Joint Undertaking

- Tripartite: Commission Participating states Industry associations

- Associations: AENEAS, INSIDE, EPoSS

- Started: 30 November 2021 (ECSEL JU -> KDT JU)

- Budget ambition : 6B€

funded by 1,8 B€ (EU)+1,8 B€ (national)

- Based on new framework programme (Horizon Europe)

**Participating**

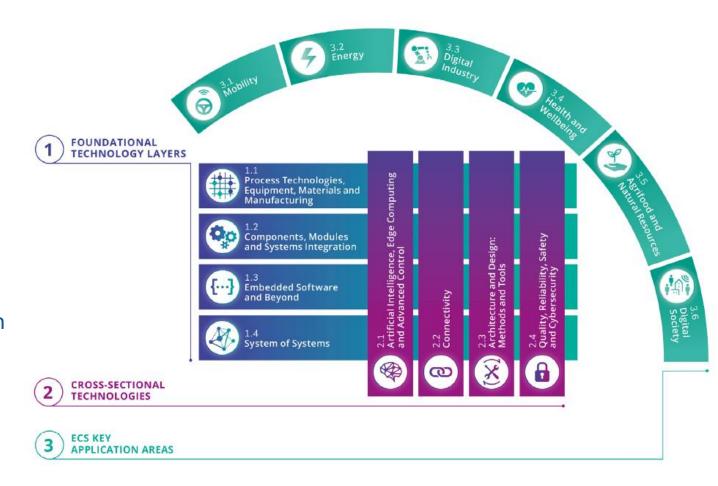

### **ECS SRIA**

- Boost industrial competitiveness through interdisciplinary technology innovations.

- Ensure/reinforce EU strategic autonomy through secure, safe and reliable ECS supporting key European application domains.

#### **BUT**

Horizon Europe stresses the importance of cooperation. There are clear potential synergies with the Photonics PPP that need to be explored.

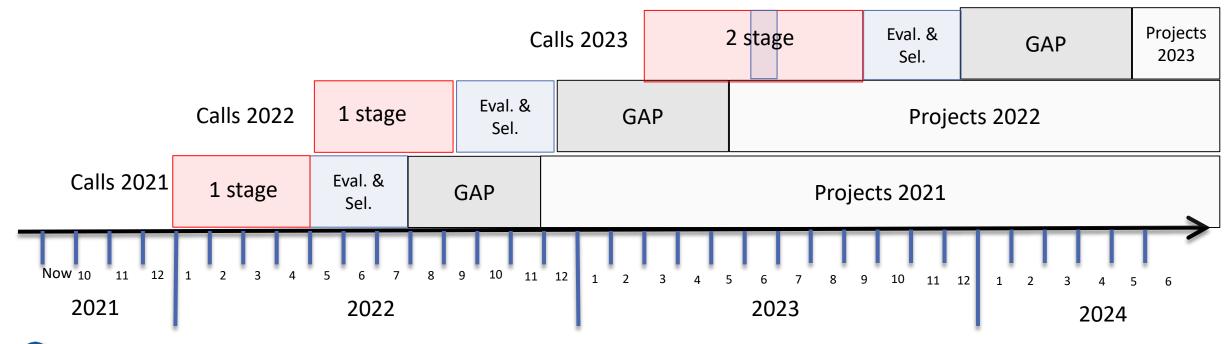

# **UPCOMING CALLS**

Caveat: no decisions yet for calls 2022 and calls 2023

Call 2022: UNDER PREPARATION

- Call RIA general and 1 Focus Topic (Green ECS)

- Call IA general and 2 Focus Topics (Photonics Line and RISC V)

Check out our website and call webpage

https://www.kdt-ju.europa.eu/current-call

- Focus topic = Top down approach

- Title (tentavely): Industrial supply chain for silicon photonics (IA)

- Type: IA = higher TRLs = towards industrialization at end of project is 8 for the industrial pilot line and TRL 6-7 for the other outcomes

#### Introduction:

- need for agile wafer-scale technologies for the heterogeneous integration of chiplets or materials that leverage

the current silicon photonics legacy

- European RTOs have developed state of the art pilot lines for this technology and are capable of low volume manufacturing. But **industrial capacity is largely missing**.

- Bringing this technology to industrial scale is a challenge but there is urgency and it befits the objective of the KDT

JU to reinforce the Union's strategic autonomy in electronic components by supporting the fast transfer of

technologies from the research to the industrial environment.

- Proposals should also lay the **groundwork for future exploitation and further enhancements**.

- The efforts should accelerate the transfer from low volume manufacturing to large volume manufacturing and render it accessible to a wider community. If successful, those could be supported by future calls within KDT and/or other programs.

#### **Expected outcomes:**

- Industrial manufacturing capability for current and next generation silicon photonic integrated circuits (PICs).

- Industrial value chains for products that address major global challenges in e.g. mobility, health, digital communication, computing and environmental sensing. This includes **specialized equipment** (e.g. metrology, epitaxy, packaging), **innovative processes**, **advances in packaging** for Systems in Package that contain photonic components. Development of **supply chains for heterogeneous silicon photonics**, reinforcing Europe's innovation potential, boosting its competitiveness, and **ensuring technological sovereignty** in this field.

- Develop agile heterogeneous PIC platforms of separately manufactured components or CMOS-uncommon materials onto silicon photonics wafers (wafer-level heterogeneous integration) that provide enhanced functionality and improved performance for a wide range of functionalities and high-value markets geared to higher TRLs and prepared for transfer to the industrial platforms.

- Photonic Design Automation software of industrial grade based on Procees Design Kits (PDK) for PICs.

#### Scope

- establish a (eventually distributed) industrially based pilot line for a silicon manufacturing platform covering

front and back end, integration and packaging (SiP) as well as wafer-level-test, chip testing, device testing to

industrial standards.

- enable breakthroughs in silicon PIC platforms, overcoming their current limitations, by wafer-level heterogeneous integration of CMOS-uncommon materials or processed chiplets and prepare the transfer to the industrial silicon manufacturing platform.

- At least two demonstrators should be built including PICs made on the pilot line covering distinctive high volume applications such as LIDAR technology, consumer medical applications, etc.

#### This pilot line **shall include innovations** such as:

- develop **innovative approaches to manufacturing techniques** for heterogeneous integration, considering judicious choices with respect to scaling, performance, alignment accuracy, agility, reliability, non-recurring engineering costs (NREs), market potential.

- develop associated photonic process design kits (PDKs) of industrial grade and make a start to automated photonics ICs design tools

- develop innovative solutions to packaging and system in package appropriate to PICs

#### Proposals are encouraged:

- to allocate tasks to **cohesion activities** (if relevant) with the projects selected under the call HORIZON-CL4-2021-DIGITAL-EMERGING-01-07: Advanced Photonic Integrated Circuits (RIA)

- organise activities **promoting the cooperation** between the KDT JU and the European partnership for photonics,

- to develop a **service-offer that will allow SMEs** and other interested organizations to prototype and manufacture PICs